IBM a présenté la semaine dernière qu'il avait développé la capacité de donner aux puces des transistors de 2 nm. La situation actuelle avec les beaux-arts se situe généralement autour de 5 nm ou 7 nm, c'est donc un saut incroyable, malgré le fait que l'évaluation des tailles entre différents fabricants n'est pas toujours correcte.

Plus accrocheur que leur taille, ces puces seront probablement développées avec un prétendu plan de 'nanosheet'. La plupart des transistors chics sont fondamentalement fondés sur 'FinFET', l'endroit où les flux de courant via l'intérieur du semi-conducteur sont étendus directement dans un équilibre. Les transistors nanosheet ou «gate-all-around» retournent cet équilibre directement dans une pile de bandes individuelles spécifiques, et le plan devrait être en mesure d'améliorer l'efficacité énergétique et de laisser les conceptions plus considérablement modifier {les propriétés électriques} de différentes parties de la puce . FinFET est typique depuis 2011, donc montrer un nouveau modèle de semi-conducteur en plastique est un arrangement sensiblement énorme dans le monde des semi-conducteurs.

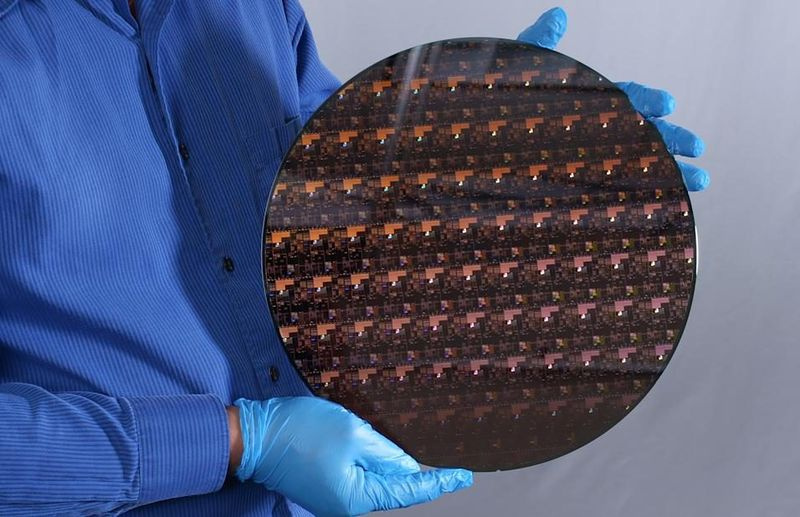

Dans un bond en avant significatif, IBM a annoncé la première puce de 2 nm de son genre dépendante de l'innovation des nanofeuilles. L'organisation a déclaré que cette puce aiderait à faire progresser le secteur des semi-conducteurs et à prendre en compte son intérêt en développement pour les puces. Les processeurs 2nm peuvent quadrupler la durée de vie de la batterie des PDA. En utilisation normale, la batterie du téléphone peut durer jusqu'à quatre jours. La puce offre 45% de mieux et utilise 75% d'énergie en moins que les puces de nœud 7nm les plus exceptionnelles actuelles.

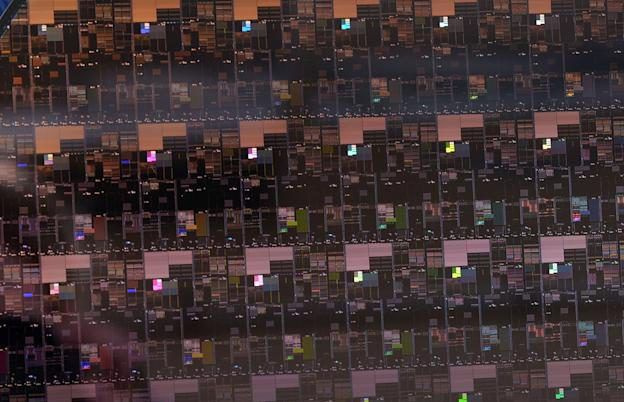

Le mélange force / exécution accélère la tournure des événements et la transmission des étapes intellectuelles, de pointe et autres étapes informatiques de pointe transmises par des conditions de cloud croisé et des pédales d'accélérateur de cryptage travaillées pour fonctionner avec des PC quantiques. La nanotechnologie de 2 nm peut utiliser jusqu'à 50 milliards de transistors sur une puce de la taille d'un ongle. Plus de transistors sur une puce permettront aux créateurs de développer des responsabilités de pointe telles que l'IA, le cloud computing, la sécurité renforcée par le matériel et le chiffrement.

La nouvelle contribution d'IBM est encore au stade de la vérification de l'idée et pourrait prendre un certain temps avant qu'elle ne soit accessible commercialement. À l'heure actuelle, les organisations adverses d'IBM, Samsung et TSMC, livrent des puces de 5 nm dans leurs fonderies. TSMC avait déclaré auparavant qu'il commencerait à fournir des puces 4 nm avant la fin de 2021 et produira des puces 3 nm en continu pendant 50% de 2022. Les puces 7 nm d'Intel sont encore en cours de développement.

Comment IBM l'a-t-il imaginé ?

Le terme nanosheet a été créé pour la première fois dans les laboratoires IBM en 2012 lorsque son groupe de spécialistes s'est occupé d'une autre ingénierie de gadgets. L'objectif était de construire une option appropriée pour la structure de nanofils grand public. La deuxième Eureka d'IBM a accompagné l'ingénierie des nanofeuilles, qui offrait les avantages électrostatiques des nanofils ainsi que l'épaisseur nécessaire pour une meilleure exécution.

Avec ce mélange de points forts, les nanofeuilles ont conquis FinFET, une structure semi-conductrice dominante à ce moment-là. Dans tous les cas, l'entreprise dépassait rapidement le plan FinFET. Les planificateurs ont essayé d'emballer plus de transistors, mais cela a entraîné un déversement de semi-conducteurs.

L'innovation FinFET tire son nom de la construction FET et ressemble à un tas de lames. Dans cette construction, les électrons traversent de délicates lames verticales, plutôt qu'une surface plane, pour traverser les transistors. Là encore, les nanofeuilles empilent les transistors les uns sur les autres pour façonner des conceptions en couches. Le semi-conducteur principal de 2 nm est le nouveau gadget de tension à seuils multiples (Multi-Vt) avec des niveaux de déversement dépassant des tailles de trois ordres. Il permet aux fabricants de choisir un degré d'exécution supérieur.